2021.03.29

FPGAに関わるASIC屋が、今すぐ知っておきたい量産FPGAの世界(3) ASIC屋が知っておきたい「FPGAのクロック経路ってどう扱うの?」

#FPGA #ASIC #LSI #クロック #スキュー #座談会

トップ > 技術ナレッジのアーカイブ > FPGAに関わるASIC屋が、今すぐ知っておきたい量産FPGAの世界 > FPGAに関わるASIC屋が、今すぐ知っておきたい量産FPGAの世界(3) ASIC屋が知っておきたい「FPGAのクロック経路ってどう扱うの?」

2021.03.29

#FPGA #ASIC #LSI #クロック #スキュー #座談会

1987年よりLSIに携わる。入社後、論理シミュレーションし試作品の作成、LSIのテスターで電気的特性の評価といった一連の業務を担当。その後タイミング設計と論理設計を15〜20年間従事する。

当初はgate arrayだったが、その後特定用途向けのASICの開発、論理設計だけでなくお客様との折衝も担当し30年ほど関わる。

半導体メーカーにてLSI設計開発

主にキャッシュディスペンサー・自動改札機・航空券発券機・PCのCD-RAMドライブなどの製品に関わる。

2000年10月 テクノプロ・デザイン社に入社

・自動車向け、エンジン制御・エアバッグ Etc マイコン設計開発

・ディスプレイ搭載回路基板設計開発、FPGA設計に従事。

仕様設計-詳細設計-試作-量産まで携わる。

また、現地中国人(上海)設計者指導、教育、アドバイザーまで様々なプロジェクトに関わる。

・2017年4月 CDA(キャリアデザインアドバイザー)着任

支店技術部組織構築補助、技術社員(エンジニア)のスキルアップ支援

株式会社テクノプロ テクノプロ・デザイン社

1997年 株式会社テクノプロ テクノプロ・デザイン社に新卒入社

人工衛星回路設計・ECU装置設計など約20年経験

現在、採用部門部長

髙島 ー

もう一つの疑問があります。

FPGAのタイミング設計ではクロック経路をどのように扱うのか、という点です。

FPGAは到達時間のばらつきを抑える物理的な構造として、クロック経路が網目になっているということですが、ASICにも「クロック経路の共通化」をしてスキューをなるべく少なくしバラつかせない、という設計をしています。

北原 ー ASICは太いクロックのラインみたいなのがあって、そこに魚の骨のように広がってるようなイメージですか?

髙島 ー

それは設計によってどうなるかわからない、というところですね。

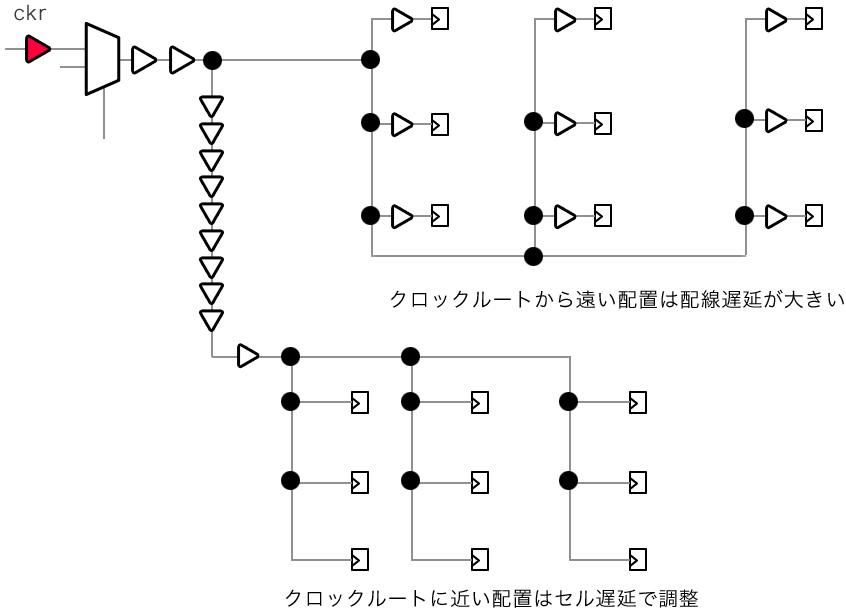

以下の図のようにクロックルートから遠いものと近いものがあるような状態が起きないことが理想的。同じ転送で同期設計されていると、ある条件ではピッタリ合ってたとしても、だんだんずれていきます。こういった設計は避けたいですね。

あとは 分岐をなるべく減らすことでクロックスキュー減らしばらつきを抑えようとと。

上図のように左下のクロックラインにはたくさんのバッファがあるのですが、これらには、ばらつき要因があるので、それを補うように厳しめに見る必要があります。

本来分岐がなく共通化できれば、条件は同じなのでバラつきは起き得ません。

だからASICの場合、クロックスキューを減したクロック経路をどうやって実現しよう、と考えるんですね。

FPGAの場合はすでにそこの設計は網目状の構造で出来上がっているので解決されている、と捉えました。ただ、網目状とはいえ、例えば右上と左下でも同じ部品ではないので、本当に一致してるかというと、まだちょっと疑問がありますけどね。

坂野 ー

FPGAの場合、端と端でも到達時間は同じ、これは信じて大丈夫です。

なぜかというと、FPGAは配置配線を論理回路に基づいて回路を配置するんですね。それにはルールがあって、例えば一つのクロックラインにフリップフロップみたいな同期回路はファンアウト、例えば3つしか置かないよ、あるいは6個以上は置かないで別のクロックラインから引っ張ってくる、みたいな判断を自動で行うんです。

例えば一本のクロックラインに10個ぶら下がっているのに、かたや別のクロックラインには1個しかない、こういう配線はしません。均等にクロックが分配されるよう調整されます。

髙島 ー

FPGAはクロックの経路を考えて、うまく調整してるような気はするけど・・・。

網目状にクロックが組んであって、例えば左上にPLL、データ出し側のffがあって受け取り側のffが右下にあった場合、それぞれPLLからの距離は異なる上に、上図の赤い部分(ドロップが大きい部分)を通る時とそうでない時でやはり電圧のばらつきがあるから、そこをどうしてるのかなと。